DS1302计时芯片和串行通信

我的FPGA开发板上有一个DS1302芯片,这是Dallas公司生产的计时芯片。它可以记录年、月、日、星期、时、分、秒信息,并且可以在断电时通过后备电源(电池)保持时钟的运行。

所以我打算利用这个芯片的功能做设计一个数字钟电路。首先需要解决的问题是和该芯片的通信。DS1302采用串行端口进行通信,因此我需要研究进行串口通信的方法。

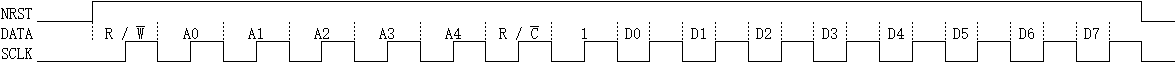

研究DS1302的通信时序图,

看似简单的时序图其实包含了大量的信息,值得仔细地研究。

首先可以看出,DS1302通过三个引脚与主机通信,分别是

NRST片选信号,用于启用/禁止串行通信。DATA数据信号,传输输入/输出数据。SCLK串行时钟信号,用于控制串行通信的节拍。

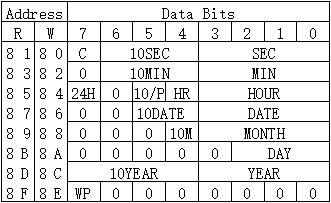

每次与DS1302通信传输2个字节,第1个字节是控制信息,表明是要进行读或者写操作,读写哪一个寄存器。第2个字节是数据信息。这两个字节的取值可以参考下表。

大体上说,DS1302是以BCD码的形式表示数据的。这样便于直接显示到数码管上,但是不便于计算机处理。

回头仔细研究时序图,可知如下的要领:

- 写入时,主机在SCLK下降沿设置DATA,从机在上升沿采样。

- 读取时,从机在SCLK下降沿设置DATA,主机在上升沿采样。

简言之:下沿写,上沿读。

根据这个规律,可以编写一个状态机。在每个状态下将SCLK翻转两次,并且在每个下降沿时刻,将下一个上升沿应当写入的比特送到DATA引脚。状态机的思想非常有用,运用它既可以设计出时序逻辑电路,又可以设计出计算机程序。

如果是构建一个时序逻辑电路,还需要注意一个问题:DATA引脚是双向引脚,读和写的寄存器都会连接到这个引脚。这个时候,需要在写寄存器的输出端放置一个三态门,当处于读的过程时,三态门应当处于高阻态,阻断输出寄存器的信号,以防和DATA引脚的输入信号发送冲突。

串行通信调试成功之后,应当注意:上电时,计时器可能处于暂停状态,这是由秒寄存器的最高位C控制的。当C=1时,计时暂停,芯片进入低能耗状态。为了能使计时器正常工作,需要设置C=0。

设置C=0之前,还要确保芯片的写保护是关闭的。将地址为8E的寄存器的最高位WP设置为0,就关闭了写保护。

因此,初始化工作应该是这样的:

- 关闭写保护。

- 设置年、月、日、星期、时、分、秒信息。

- 将秒寄存器的最高位设置为0,计时开始。

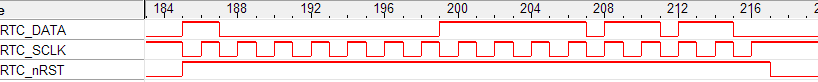

顺便一提,Quartus Prime软件提供的Signaltap II逻辑分析仪无比好用。用它可以像使用真实的逻辑分析仪那样,观察各个引脚的信号值,甚至可以观察到FPGA内部节点的信号值。这对于调试电路来说是有巨大的帮助的。